| 一步一图,带你全面了解模拟芯片设计流程 | 您所在的位置:网站首页 › 版图 dummy diff › 一步一图,带你全面了解模拟芯片设计流程 |

一步一图,带你全面了解模拟芯片设计流程

|

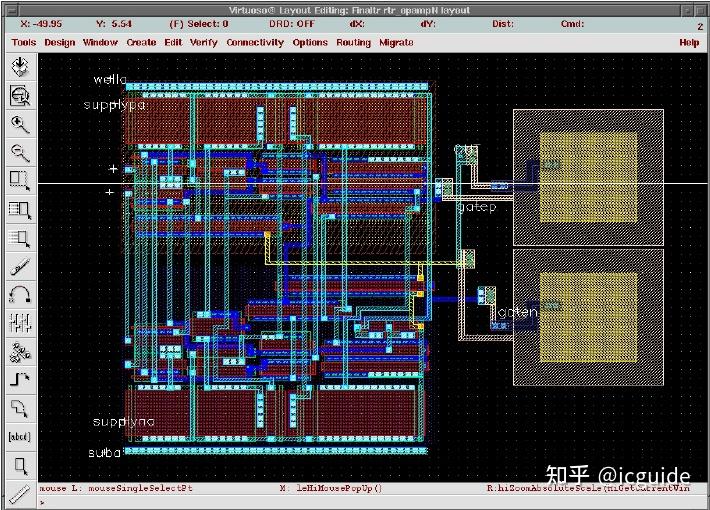

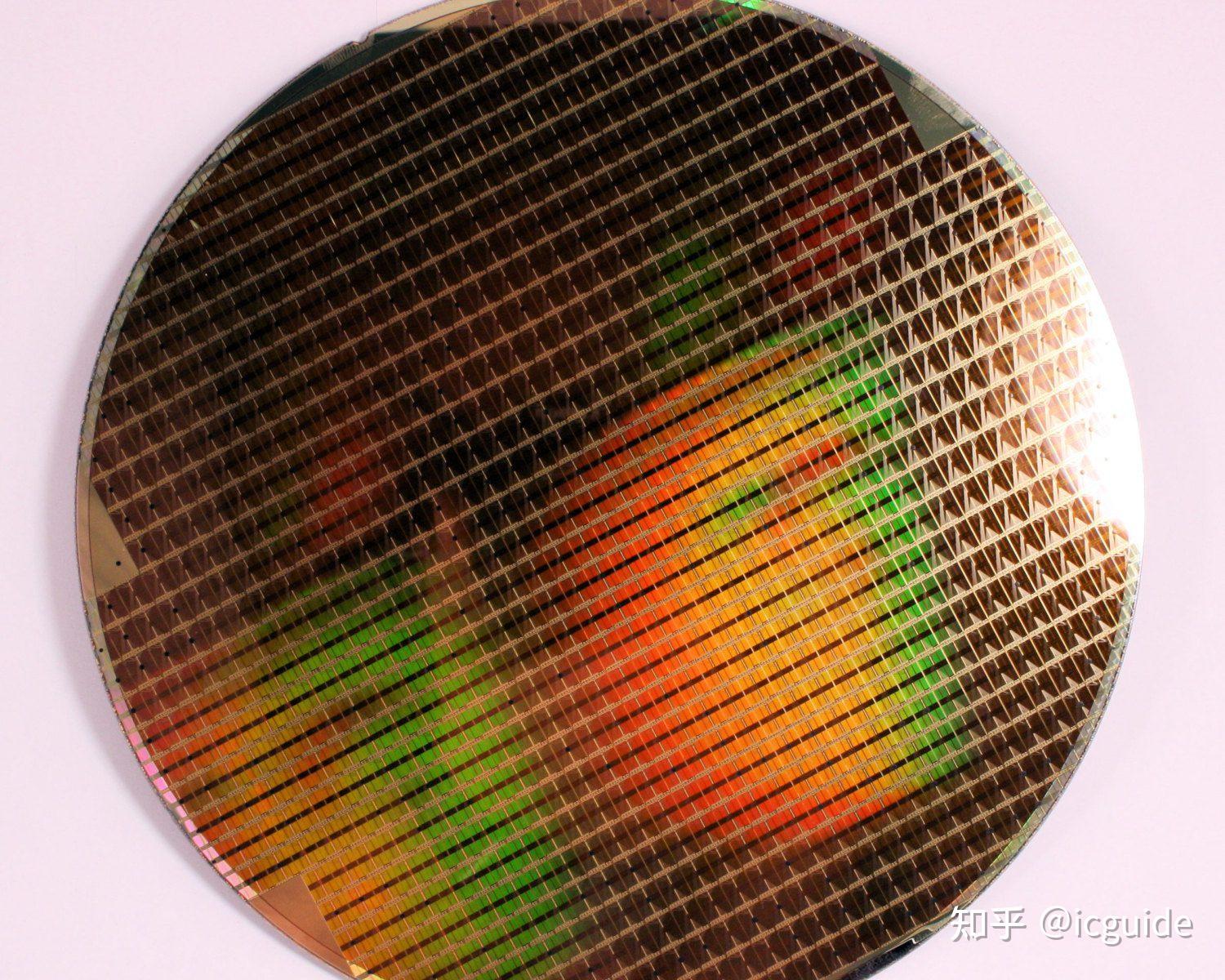

前言 模拟模拟,模拟两可 江湖总是流传着模拟难学的传说,模拟芯片设计难点主要可以总结为如下几点: 器件参数 模拟电路的性能与器件参数密切相关。在模拟电路设计中,需要选择合适的器件,并制定相应的工艺和制造流程,以满足要求的性能和可靠性。跨越多个学科 模拟电路设计融合了电子学、电路理论、传输理论、控制理论等多个学科知识。因此,设计师需要具备广泛的专业背景和丰富的经验才能有效解决各种问题。噪声和干扰 模拟电路常常面临噪声和干扰的挑战。这些噪声和干扰源可能来自于器件本身、周围环境或其他电路的干扰等。因此,设计师需要采取一系列的技术手段来降低噪声和干扰,如噪声抑制、屏蔽措施等。快速变化的信号 模拟电路中的一些信号往往快速变化,例如高频振荡信号、瞬态响应信号等。设计师需要选择合适的电路结构和器件参数,以保证信号的稳定性、准确性和可靠性。仿真和验证 模拟电路设计需要进行比较复杂的仿真验证。由于实际电路中会存在很多非理想因素,因此需要进行大量的仿真和分析,以确保电路的性能和工作状态达到要求。虽然很难,但是大师们却又都说模拟设计中蕴含着巨大的魅力,令人神往。 下面开始我们介绍模拟芯片设计的整个流程,看能否激起大家都模拟芯片设计的兴趣 总览 模拟芯片设计流程分步详解电路图设计 模拟芯片设计流程分步详解电路图设计电路设计基本技能要求: - 掌握基本的电路理论和分析方法,包括放大器、滤波器、稳压电路等。 - 熟悉各种主要的模拟电路元器件,如运算放大器、电阻、电容、二极管等。 - 了解各种模拟电路的设计方法,例如反馈电路、比较器电路、振荡器电路等。 - 具备良好的模拟电路设计经验和实践能力,熟悉常用的电路仿真和分析工具,如LTSpice、PSpice等。 在进行模拟芯片的电路图设计时,通常需要根据所需功能和性能要求来确定电路结构和参数,然后使用相应的电路设计工具进行模拟和验证,不断进行调整和优化,直到满足设计要求为止。 以candence为例,电路图编辑界面如下所示:  电路图设计版图设计 电路图设计版图设计模拟版图设计的要点包括: 确保规范的工作环境,包括合适的灯光、通风等条件。根据设计要求选择合适的工艺库(Process),例如TSMC、UMC、SMIC等。了解器件库(Cell Library)中每个元件的特性和参数,以及如何使用和调整它们。选取合适的雷电保护、ESD保护和EMC设计措施。进行DRC(Design Rule Check)、LVS(Layout Versus Schematic)等验证工作,确保设计符合工艺规范和原理图。合理布局,如摆放具有相似功能的电路元件,并使用dummy管等技术来减少阱偏效应等影响。执行信号线编辑和优化,缩短信号传输路径和降低信号衰减。优化功耗、面积和性能等指标,如采用代价函数、自动布线等技术。在进行模拟版图设计时,常用的EDA工具有Cadence Virtuoso、Mentor Graphics等  版图设计规则检测:DRC&LVS 版图设计规则检测:DRC&LVSDRC原理: DRC是一种基于设定的规则来检查版图设计是否符合特定规范要求的工具。它可以检测到许多设计问题,如过程偏差、器件数太少或太多、深尺寸过小等。在DRC检查完成后,会生成一个错误列表,其中包含所有未满足规则的设计部分。设计人员需要对这些问题进行逐一排查和解决,以确保设计符合规范。  DRC DRCLVS原理: LVS是一种将原理图与版图进行比较的工具,以确保它们之间的一致性。它使用电路仿真技术来识别并修复原理图和版图之间的任何匹配问题。在这个过程中,会检查元件名称、数量、大小、连接等信息,以确保版图反映了原理图的正确性。如果存在不匹配的情况,LVS将生成一个错误报告,列出两个文件之间的任何不一致之处。  LVS LVSDRC和LVS用途: 在模拟电路设计中,DRC和LVS通常是版图设计的最后一步,以确保设计的正确性和可制造性。通过使用DRC和LVS,设计人员可以检查布局是否符合特定的规范,以及电路是否与原理图一致。通过这种方式,可以帮助设计人员在制造之前及时发现错误,并提高设计自动化的水平。 布局规划:Floor Planning intel cpu的布局规划 intel cpu的布局规划规划时需要考虑的因素: 电路模块的大小、形状和样式;各个模块之间的通信和交互方式;模块之间的布线需求;器件和引脚的位置和数量;电源和接地网络、射频层、信号间隔等不同层次的要求;内存和缓存的配置和布局等。Floor Planning工具常用功能: 手动布局和自动布局;可调整大小和旋转的单元格;与其他EDA工具的集成,如DRC、LVS等;外部文件导入和导出等。通过Floor Planning工具,设计团队可以快速测试和优化芯片的不同布局方案,并评估每个方案的优缺点,以找到最终的布局解决方案。 Dummy 填充 dummy 填充以及优化 dummy 填充以及优化作用: Dummy填充主要用于解决一些物理效应,如阻抗、反向漏电和漏电流等,提高芯片的电气性能和可靠性。 设计时需要注意的要点: 确定填充的目的和需求:在进行Dummy填充设计之前,必须明确所要解决的问题以及Dummy填充的具体目的和需求。这些可能包括电气特性的改进、阻止异相偏差、防止膨胀和收缩等。确定填充的形状和大小:根据具体的需求,确定填充所需的形状和大小,通常采用矩形或多边形的形式,并根据层数的需要进行调整。在合适的位置添加Dummy填充:在芯片版图中添加Dummy填充的位置通常包括行末、列末和芯片的四周。还可以在一些特定的区域添加Dummy填充来解决一些特定的物理效应。避免不必要的Dummy填充:在设计过程中,为了避免不必要的花费,应尽量减少Dummy填充的数量并保持整洁。此外,Dummy填充应该保证在不影响布局和可靠性的前提下尽量减小面积和长度。进行DRC和LVS检查:Dummy填充的设计过程中,需要进行DRC和LVS等验证以保证填充的正确性和可制造性。版图后DRC&LVS post layout post layout注意的事项: 版图设计规则:在进行DRC和LVS检查之前,必须准确了解所使用的每个工艺库的规则和限制,并按照这些规则执行版图设计。保证版本一致性:在进行DRC和LVS检查之前,必须确保版图和原理图版本是一致的,并且版图正确地表示了原理图的所有元件和连接方式。前置检查:在运行DRC和LVS之前,必须进行前置检查,包括检查器件的尺寸、电容和电感等参数的正确性,并确保网表模型和LVS模型的一致性。设置DRC和LVS规则:在进行DRC和LVS检查之前,必须明确设置每个规则和限制,以确保可以准确地检查设计中存在的问题。运行DRC和LVS检查:在设置好规则和限制后,运行DRC和LVS检查以识别和解决任何物理设计错误和电路不一致问题。解决错误:如果在DRC和LVS检查中发现任何错误,则必须及时对错误进行分析和解决,并确保设计的正确性,并再次运行DRC和LVS检查以验证修复后的版本。GDS文件 GSD文件全称是"Geometry Summary Data",是半导体工艺模拟软件中的一种输入文件,它包含有关芯片结构、形状和层次结构的几何数据。GSD文件用于定义芯片的三维结构和电学特性,作为模拟器模拟和仿真的依据。GSD文件包含信息: 层次结构和顶层结构:GSD文件描述芯片的不同层和顶层结构,包括金属层、多晶硅层、掩膜层、胶片层等。几何信息:包括芯片各个部位的尺寸、形状、位置以及与其他部位的连接方式等。特殊功能区域:如联排、防抖动区域、纹理区、DPJ (Diffusion Pocket Junction) 等。材料属性信息:描述每个层的材料类型、介电常数、厚度等。GSD文件可以通过不同的软件生成,如Tanner L-Edit、Cadence Virtuoso等。 生成GSD文件后,需要根据需要,将GSD文件转换为其他格式,如SPICE模型,以进行进一步的仿真和分析。 总之,GSD文件是半导体工艺模拟软件中的重要文件,它是芯片设计和制造中的关键部分,可以提供有关芯片结构和几何信息的详细描述,并为后续的仿真和分析提供依据。 流片:tape out 流片 流片注意事项: 设计规则检查 (DRC) 和物理验证 (LVS):在进行tape out之前,一定要进行完整的设计规则检查和物理验证,以确保设计符合制造商的要求和规范。芯片层次结构:确保芯片的层次结构和版本信息准确无误,并且与制造商的要求相符。校准格栅:在进行芯片tape out时,需要给出正确的校准格栅信息,确保制造商能够准确地定位电路的位置和大小。资料提交:确定自己持有所有必需资料,并且资料表单已提交并审核。版本控制:确保在进行tape out之前,对于设计中的所有版本和更改都做好了记录,并且能够轻松地跟踪每个版本的变化。封装和引脚:确保所选用的芯片封装符合制造商要求,芯片的引脚数和位置准确无误。确认生产计划:在进行tape out之前,确定芯片制造商的生产计划和时间表,以确保在规定时间内收到芯片。安全:确保在进行tape out时,数据的安全性得到保证,如加密文件、签名等。硅后测试验证 硅后测试 硅后测试硅后测试验证通常包括以下几个方面: 功能测试:检测芯片是否按照设计的预期功能正常工作。电学测试:使用各种测试方法进行检测,例如直流参数测试、AC 参数测试、功耗测试、时钟测试等等。可靠性测试:测试芯片是否满足产业标准或者芯片制造商自己的规范要求,例如温度、压力、湿度等环境测试,以及EMI/EMC、ESD、LATCH UP等测试。系统级测试:将芯片整合到完整系统中,并进行测试检验。硅后测试验证是确保芯片在制造和生产中的正确性和效率的重要步骤。然而,硅后测试验证也存在着一定的成本和时间。因此,在设计阶段时,应该尽可能全面地考虑芯片在制造和生产过程中可能遇到的问题,并预先设计出可靠、稳定的芯片设计方案,以减少芯片硅后测试验证的成本和周期。 ECO和量产Engineering Change Order(ECO) 是指在生产过程中,由于设计变更、工艺变化或其他原因导致的芯片重新加工和测试的过程。设计变更:芯片 ECO 设计要点之一是设计变更。在设计变更时,需要对芯片的电路图、版图、工艺参数等进行修改和优化,以确保芯片的质量和生产效率。设计变更需要遵循生产工艺和规范,以确保芯片的稳定性和可靠性。工艺变化:芯片 ECO 设计要点之二工艺变化。工艺变化可能导致芯片的布局、封装、测试等方面的变化。工艺变化需要根据新的工艺要求进行设计和优化,以确保芯片的质量和生产效率。批量测试:芯片 ECO 设计要点之三批量测试。在芯片 ECO 过程中,批量测试需要重新进行,以确保芯片的质量和可靠性。批量测试需要遵循新的测试规范和要量产阶段的注意事项 生产线需要保持高度自动化和高效运作,以确保芯片的生产效率和质量。芯片的包装和标记需要准确无误,以确保芯片的可追溯性和识别性。芯片的储存和运输需要符合防潮、防振、防盗等要求,以确保芯片在运输和储存过程中不受损害。生产线需要进行严格的质量控制和检测,以确保芯片的质量和可靠性符合质量标准。后记芯片设计虽然已经很难,但是量产并不是终点。 芯片设计出来之后,还需要代理商、分销商、市场推广、评估板、FAE、产品demo、方案商等等一系列的工作,才能将芯片变成我们每个人所使用的的电子产品。 refshttps://zh.wikipedia.org/wiki/%E9%9B%86%E6%88%90%E7%94%B5%E8%B7%AF%E7%89%88%E5%9B%BEhttps://en.wikipedia.org/wiki/Design_rule_checkhttps://en.wikipedia.org/wiki/Floorplanninghttps://www.einfochips.com/blog/guidelines-for-a-successful-tapeout/https://miscircuitos.com/design-process-of-chips-asics-flow-from-design-to-tapeout/ |

【本文地址】